23 / 12 / 18

「考研记录」电子科技大学 832 微电子器件 简答题汇总

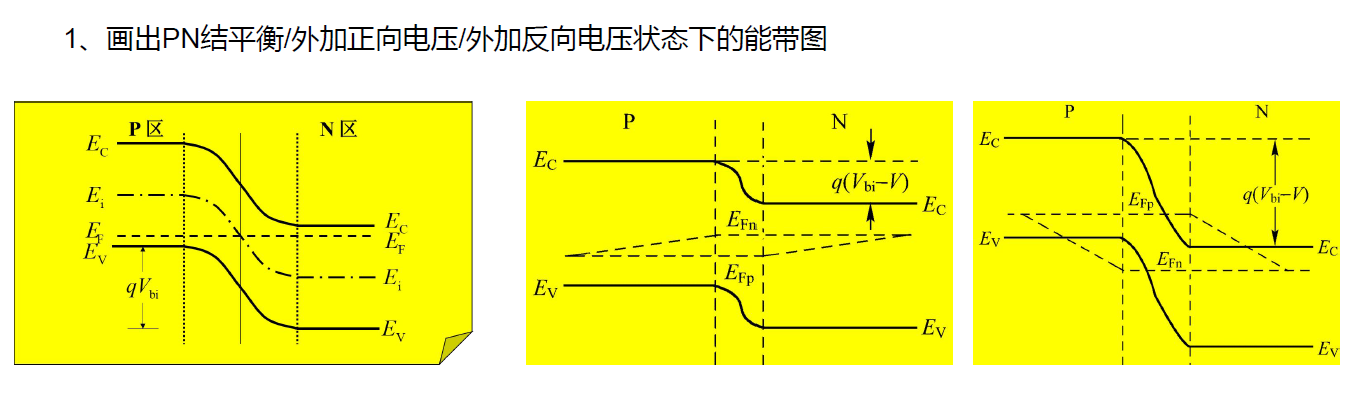

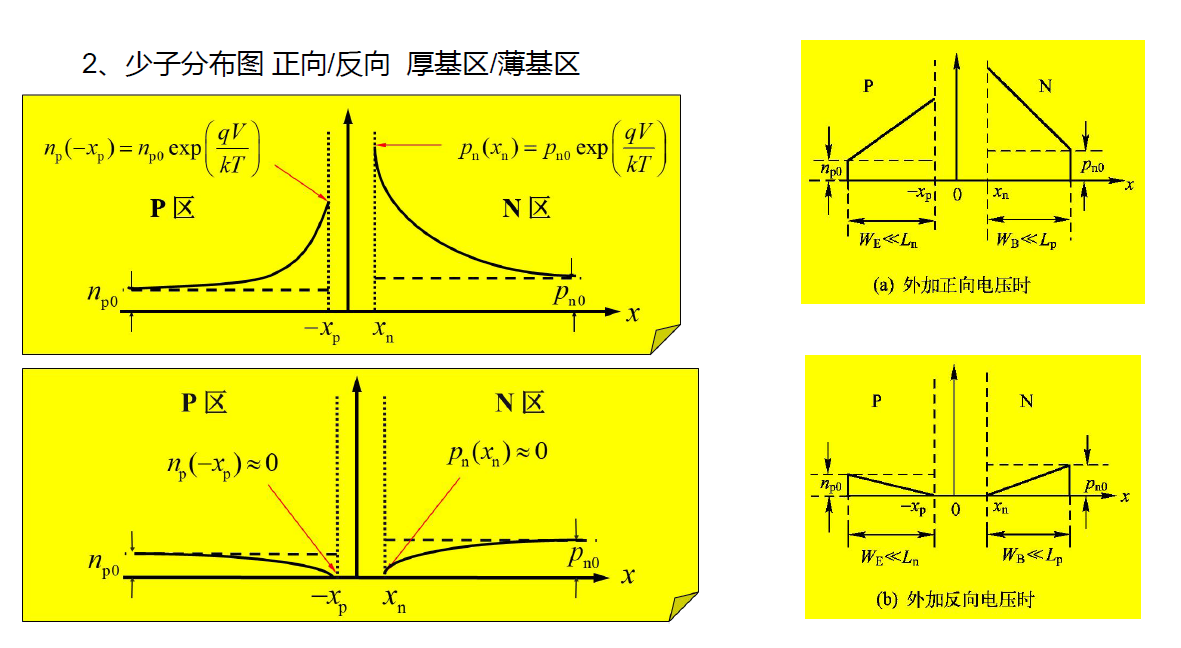

PN

1. 什么是耗尽近似?

空间电荷区内的自由载流子已完全扩散掉,即完全耗尽,电离杂质构成空间电荷区内电荷的唯一来源。

2. 什么是中性近似?

耗尽区以外区域中的多子浓度仍然等于电离杂质浓度。

3. PN结空间电荷区是怎样形成的?

P区与N区接触后,由于存在浓度差的原因,结面附近的空穴将从浓度高的P区向浓度低的N区扩散,在P区留下不易扩散的带负电的电离受主杂质,结果使得在结面的P区一侧出现负的空间电荷;同样地,结面附近的电子从浓度高的N区向浓度低的P区扩散 ,在N区留下带正电的电离施主杂质,使结面的N区一侧出现正的空间电荷。由此产生的空穴与电子的扩散电流的方向,都是从P区指向N区。

扩散运动造成了结面两侧一正一负的空间电荷区 ,空间电荷区中的电场称为内建电场,方向为从带正电荷的N区指向带负电荷的P区。这个电场使空穴与电子发生漂移运动,空穴向P区漂移,电子向N区漂移,由此产生的空穴与电子的漂移电流的方向 , 都是从N区指向P区,与扩散电流的方向相反。

随着扩散的进行,空间电荷区逐渐变宽,内建电场逐渐增强,空穴与电子的漂移运动也逐渐增强,最终使漂移电流与扩散电流相等,流过PN结的净电流为零达到平衡状态,这时空间电荷区宽度与内建电场强度也达到一个稳定的数值。

4. 解释PN结的整流特性/ PN结为什么会有单向导电性?

外加正向电压时,空穴扩散流的电荷来源是P区空穴,电子扩散流的电荷来源是N区电子,都是多子,正向电流很大;外加反向电压时,N型区空穴扩散流的电荷来源是N区空穴,P型区电子扩散流的电荷来源是P区电子,都是少子,正向电流很小。

5. 解释反向饱和电流密度的物理意义。

由于外加反向电压时势垒区边界处的少子浓度为零,N区内浓度为p_n0的平衡少子将以(D_p/L_P)的扩散速度向边界运动,形成电流密度q p_n0(D_p/L_p)。

凡是离势垒区边界一个扩散长度范围内产生的少子,均可构成电流。由千N区少子的产生率为(p_n0/t_p),因此电流密度为(q L_p p_n0/t_p),考虑到L_p^2=D_p t_p,故电流密度亦可写成为 q D_p p_n0/L_p。

P区一个扩散长度内产生的电子扩散电流密度也有类似的表达式,两个电流密度相加即可得到反向饱和电流密度。

6. PN 结大注入下的自建电场是怎么产生的,作用是什么?

由于电子不可能像空穴那样从P区得到补充,所以电子的浓度梯度绝对值要略小于空穴的浓度梯度绝对值。就非平衡载流子而言,在靠近势垒区附近的地方,电子浓度略小于空穴浓度,使这里出现了正电荷;而在远离势垒区的地方,电子浓度略大于空穴浓度,使那里出现了负电荷。电荷在空间上的分离就产生了一个自建场,其方向是从势垒区指向中性区。

7. Webster 效应是什么?

由于大注入时少子浓度与多子浓度处处相等,而且两种载流子的(D/u u)值也相等,所以宏观上阻止多子流动的电场,使多子产生和扩散方向相等,方向相反的漂移运动,那么这个电场必定使少子产生和扩散运动大小相等、方向相同的漂移运动。这相当于使少子的扩散系数D 增大了一倍。

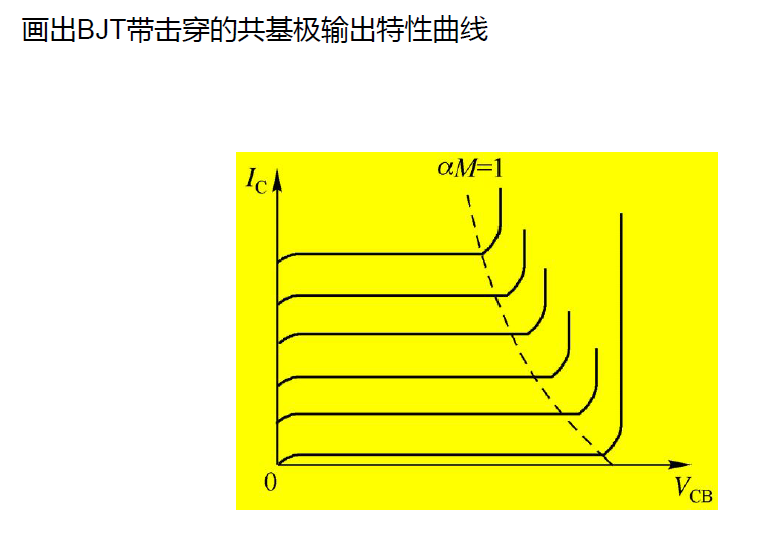

8. 解释雪崩倍增效应机理。

当电场强度增加到一定程度后,势垒区中的载流子就会发生碰撞电离而激发出新的电子—空穴对,即“二次载流子”。后者又可能继续产生新的载流子。这种过程将不断进行下去,每个载流子无止境的地繁殖新的载流子,即使初始电流很小,流出PN 结的电流也可以任意大。

9. 解释齐纳击穿机理。

当反向电压V增加到使势垒区中最大电场𝐸_𝑚𝑎𝑥达到一个临界值时,隧道长度小到一个临界值,这时大量P区价电子通过隧道效应流入N区导带,使隧道电流急剧增加。

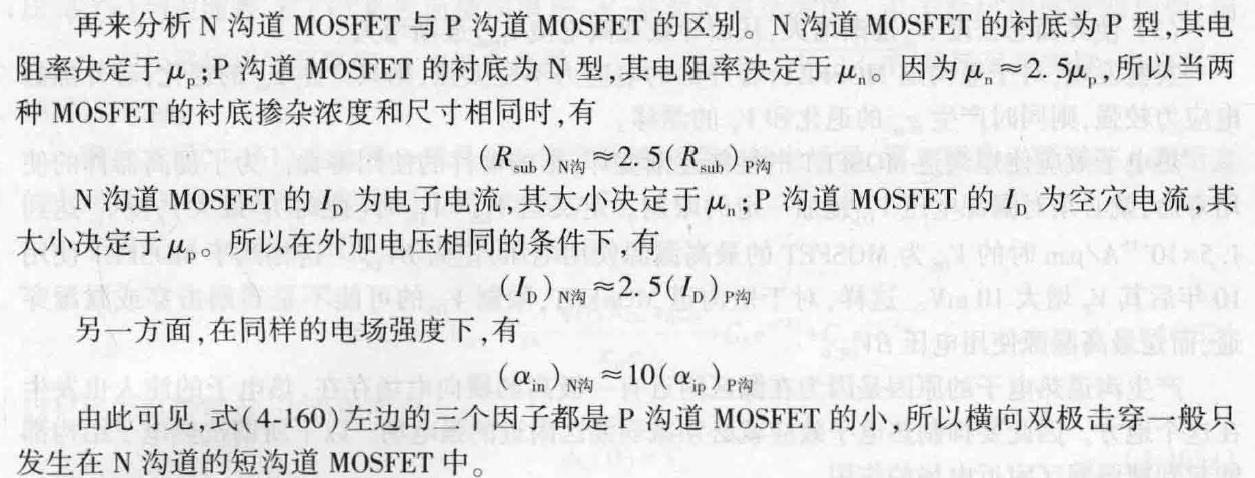

10. 比较雪崩击穿与齐纳击穿。

11. 解释稳压二极管工作原理、制作工艺选择。如何提高其温度稳定性?

可以利用PN结在反向击穿时电流急剧增大这种特性来作为稳压二极管。当电路中荫点间的开路电压超过PN结击穿电压VB时,就会有大械电流被并联在该两点间的稳压二极管所旁路,通过电源内阻的分压作用使这两点间的电压下降到接近固定的VB值。

对于6V以下的硅稳压二极管,掺杂浓度应很高,以利于发生隧道击穿,因此常采用合金法来制造。对于12 V以上的硅稳压二极管,则掺杂浓度应当稍低,因此常采用扩散法来制造。 对于电压介于上述两值之间的稳压二极管,则两种方法均可采用。

由于雪崩击穿具有正温度系数而齐纳击穿具有负温度系数,为了使稳压二极管的击穿电压尽量不受温度的影响,可以通过适当选择PN结的杂质浓度分布,使其击穿电压处于两种击穿机理兼有的范围,使两种击穿电压的温度系数互相抵消。

12. 简述热击穿发生的机理。

反向饱和电流l0正比于ni^2将随结温的上升而迅速增加,所以I0具有正温度系数。Tj的升高会使l0增加,这样就在电流与结温之间形成了正反馈。结温升高使电流增加,电流增加使功率损耗增加,功率损耗增加使结温上升,从而导致电流进一步增加。如果这一过程不受控制地进行下去,将使电流与温度无限增加,最终导致PN结器件被烧毁。

13. 什么是PN结的势垒电容?什么是PN结的扩散电容?比较PN结的势垒电容和扩散电容。

势垒电容:当外加电压发生Δ𝑉的变化时,空间电荷区宽度会发生变化,使冶金结两侧的空间电荷也发生相应的(+∆𝑄)和(−∆𝑄)的变化。空间电荷区的这种变化是多子电流对空间电荷区充、放电的结果。

扩散电容:当外加正向电压有一个增量Δ𝑉时,从P区注入N区的非平衡空穴增加,使N区内出现一个正电荷增量(+∆𝑄) 。与此同时相同数量的非平衡电子从N区欧姆接触处流入N区,以与增加的空穴维持电中性,使N区内出现一个相同大小的负电荷增量(-∆𝑄)。也就是说,电压的变化Δ𝑉引起了一对大小相等、符号相反的非平衡载流子电荷存储于N区,它们各自从两端的欧姆接触处而来,只相当于一个电容。

扩散电容:中性区中非平衡载流子电荷随外加电压的变化而变化;势垒电容:势垒区边缘处电离杂质电荷随外加电压的变化而变化。

扩散电容,只存在于正偏的情况下,不能作为电容器使用;势垒电容,正反偏都存在,在反偏下可以作为电容器使用。

扩散电容和势垒电容都是外加电压的函数。扩散电容只存在于低频的情况下。

14. 简述势垒电容与结的近似关系。

一个在较低掺杂的衬底上制备的 PN 结,如果其结深很小,浓度梯度很大,可以近似为突变结,其势垒电容与外加反向偏压的绝对值是1/2次方;一个在较高掺杂的衬底上制备的 PN 结,如果其结深很大,浓度梯度很小,可以近似为线性缓变结,其势垒电容与外加反向偏压的绝对值是1/3次方。

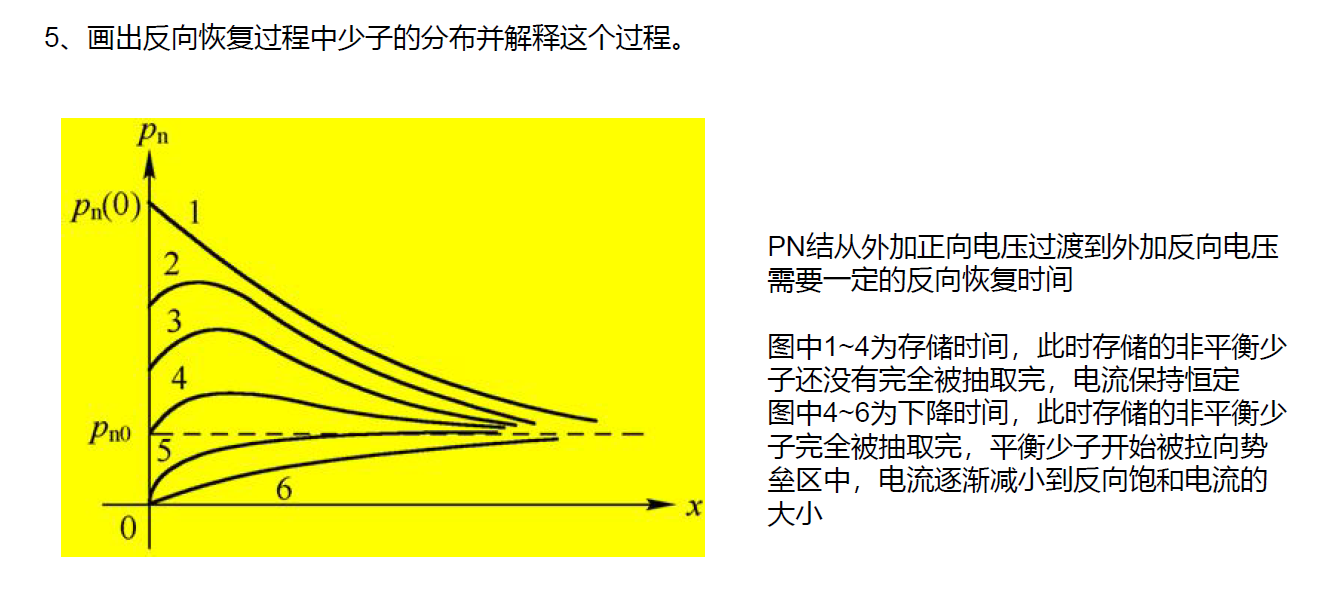

15. 简述减小PN结二极管的反向恢复时间的方法。

(1)从电路角度考虑,应使用尽可能小的正向电流𝐼𝑓,尽可能大的反向抽取电流𝐼𝑟。

(2)从器件角度考虑,应降低少子寿命。在半导体中引入复合中心可以降低少子寿命,可以采用掺金、掺铂、电子辐照、中子辐照等方法引入复合中心。

(3)减薄轻掺杂区厚度,即采用“薄基区二极管”结构。(可以减少存储电荷,最大抽取电流)

BJT

1. 什么是双极晶体管效应?

通过改变一个PN 结的偏压来控制其附近另一个PN 结的电流的方法。

2. 为什么基区要做的很窄?

如果基区宽度足够厚,即WB>>LB,则晶体管的两个PN 结之间没有相互作用,从发射区注入基区的空穴将在基区中全部与电子复合掉,转化成电子电流从基极流出。集电结则因处于反偏而只有极小的反向饱和电流。这就只是两个反向串联的二极管而不是晶体管了。

实际上晶体管的基区必须足够薄,即WB<<LB 。这时,从发射区注入基区的空穴在基区中只复合了极少一部分,绝大部分还未来得及复合就已扩散到了集电结边上,被集电结势垒区的强电场拉入集电区,形成集电极电流lC,从集电极流出。

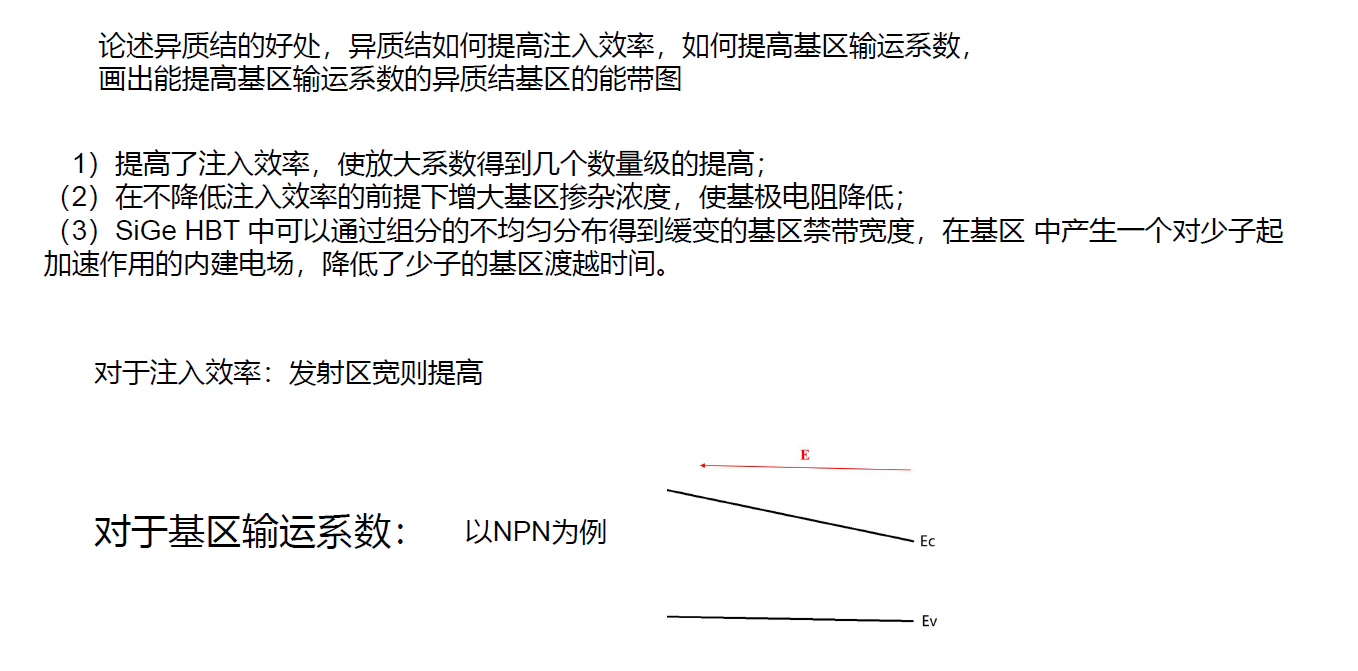

3. 论述 BJT 共基极接法IE到IC电流亏损的原因,如何衡量这两种亏损?

InE代表从基区注入发射区的电子形成的电子扩散电流,它是发射极电流的一部分、但却与集电极电流无关,这部分损失用发射结注入效率衡量。

Inr代表为补充与注入基区的空穴复合时损失掉的电子而流入基区的电子形成的电流,它与空穴在渡越基区时发生少量复合而形成的空穴复合电流Ipr相等,这部分损失用基区输运系数衡量。

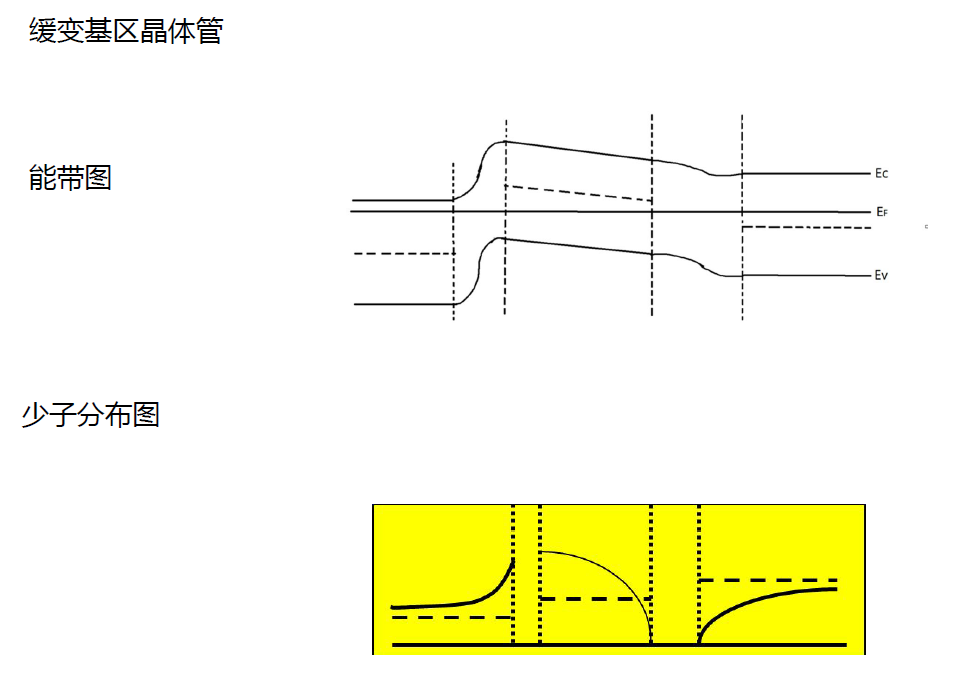

4. 简述基区内建电场的形成机理。

室温下杂质全电离,因此多子空穴有与受主杂质近似相同的浓度分布。空穴浓度的不均匀导致空穴从高浓度处向低浓度处扩散,而电离杂质却固定不动,于是在杂质浓度高的地方空穴浓度低于杂质浓度,带负电荷;在杂质浓度低的地方空穴浓度高于杂质浓度,带正电荷。空间电荷的分离就形成了内建电场。

5. 什么是发射区重掺杂效应?具体的机理有哪两种,分别是怎么影响注入效率的?

当发射区掺杂浓度过重时会引起发射区重掺杂效应,即过分加重发射区掺杂不但不能提高注入效率,反而会使其下降。

发射区禁带变窄

当发射区掺杂浓度不太大时,发射区电阻的减小作用超过禁带宽度的增大作用,注入效率随掺杂浓度的增加而先增大。但是当掺杂浓度超过一定限度后, 后者的增大作用超过了前者的减小作用,注入效率下降,导致放大系数下降。

俄歇复合增强

由于多子浓度与掺杂浓度几乎相等,这使得发射区的少子寿命在重掺杂时大为下降。此外,掺杂过重还会使载流子的扩散系数减小。发射区少子寿命与少子扩散系数的减小使发射区少子扩散长度减小,使从基区注入发射区的少子形成的电流增大,从而导致注入效率下降。

6. 什么是基区陷落效应?其产生的原因是什么?如何抑制基区陷落效应?

发射区的磷掺杂浓度很高时,会使发射区正下方的集电结结面向下扩展。

造成陷落效应的原因,在于磷的原子半径和硅的原子半径的不一致。

当硅中的磷浓度较高时,由于应力关系,会产生较多的位错,有利于形成空位,从而使该处有较高的杂质扩散系数。因此,发射区下的砌与磷都存在增强扩散。由于陷落效应,使得结深不易控制,难以将基区宽度做得很蒲。位错的存在不仅会发生陷落效应,而且由于杂质沿位错扩散较快,会造成结面不平坦,使个别地方的发射区与基区穿通或易于击穿。另外,有些重金属杂质也易于凝聚在位错附近,造成击穿电压下降。

采用砷扩散来代替磷扩散。

7. 简述砷扩散代替磷扩散的好处。

砷的原子半径与硅的相近,没有陷落效应。此外,砷扩散后的杂质分布接近于矩形,在基区中靠近发射结附近的施主与受主的补偿区域极小,使基区中的减速场区域极窄。砷扩散后的基区电阻也较小。总之,砷是一种较理想的发射区掺杂杂质。

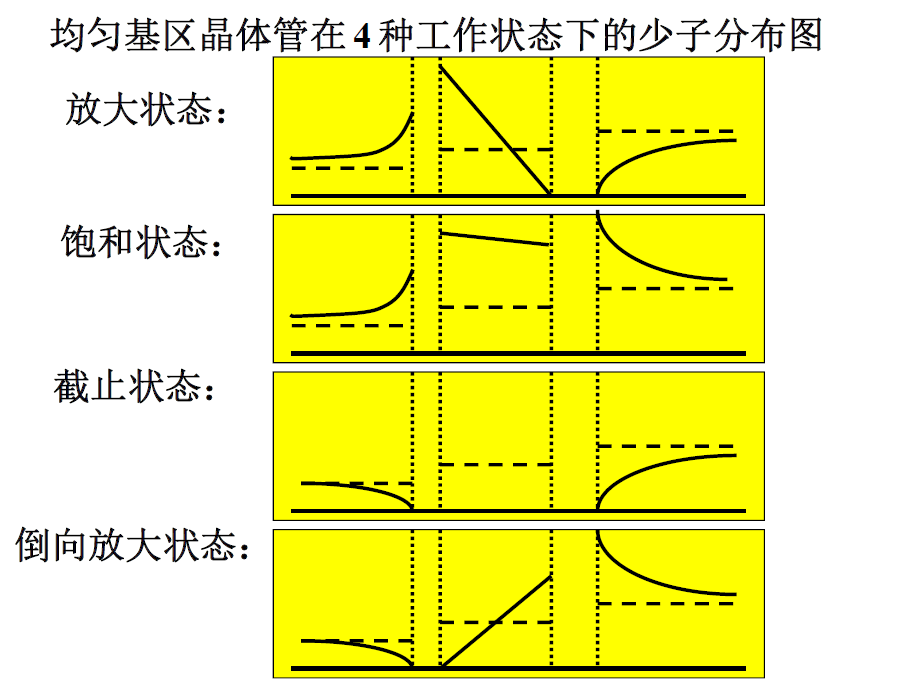

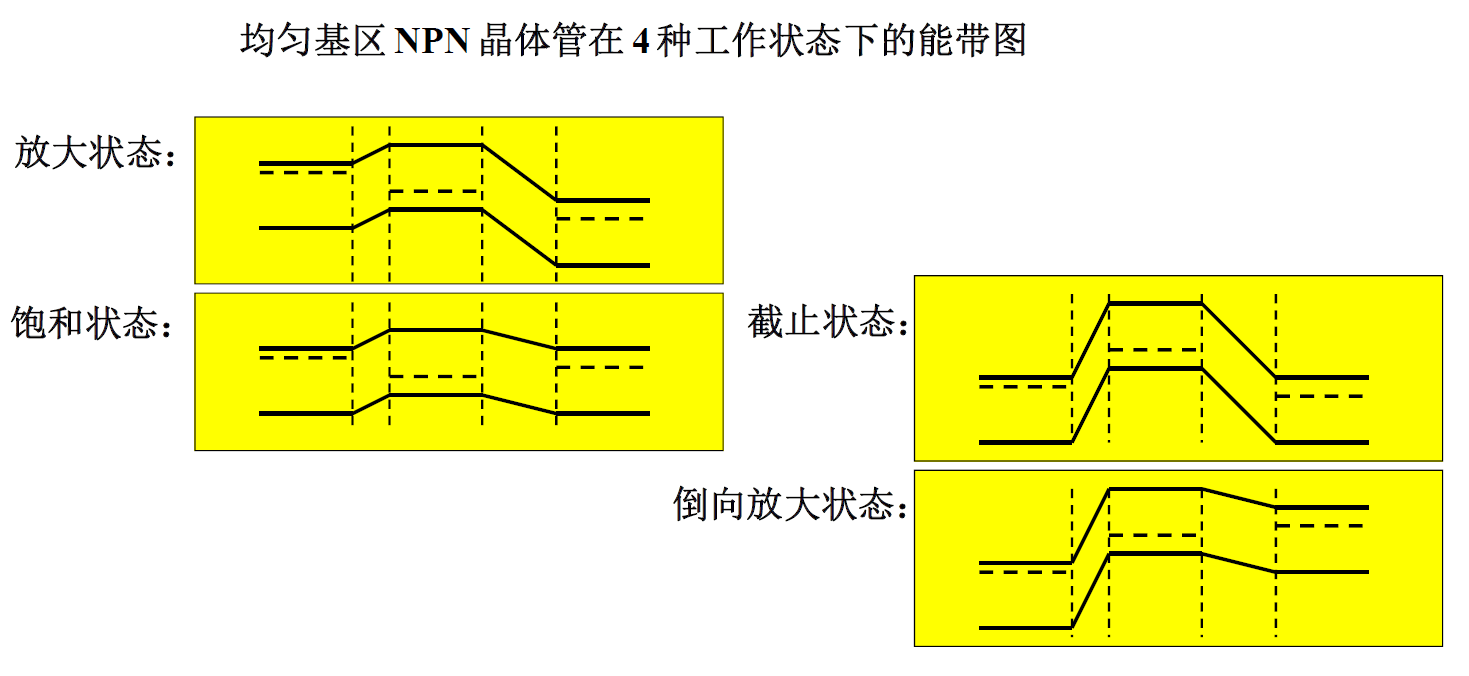

8. 简述a_R≪a的原因。

集电结的面积一般比发射结的大。在正向管中,从发射结注入基区的少子几乎能够全部被集电结所收集,但在倒向管中,从集电结注入基区的少子只有一部分能被发射结所收集;除合金管外,集电区的掺杂浓度一般低于基区,使倒向管的注入效率降低;在缓变基区晶体管中,基区内建电场对倒向管的基区少子起减速作用。

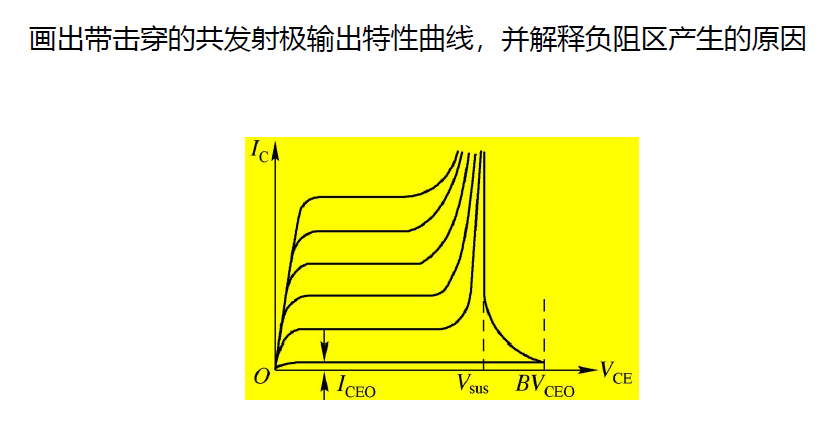

9. 简述厄尔利效应产生的机理、现象;如何抑制厄尔利效应?

当VCE增加时,集电结上的反向偏压增加,集电结势垒区宽度增宽。势垒区的右侧向中性集电区扩展,左侧向中性基区扩展。这使得中性基区宽度WB减小。基区宽度的减小使基区少子浓度梯度增加,必然导致电流放大系数和集电极电流的增大。

lc在放大区随VCE的增加而略有增加。

增大VA的措施是增大基区宽度WB 、减小势垒区宽度XdB,即增大基区掺杂浓度。但这些都是与提高电流放大系数相矛盾的。

10. 简述浮空电势的概念。

当发射极开路、集电结反偏时,基区中部分少子被集电结上的反偏扫入集电区。但因IE=0, 基区少子得不到补充,使在基区与发射结势垒区边界处,n_B(0)<n_B0 。根据结定律,这时在发射结上存在一个反向电压。

11. 什么是基区穿通,如何防止基区穿通?

当集电结上的反向电压增加时, 集电结耗尽区向两侧扩展, 基区宽度W_B随之减小。对于基区很薄且基区掺杂较轻的晶体管, 当集电结反偏达到某一值V_pt时, 虽然还没有发生集电结的雪崩击穿,但WB已减小到零,这时在发射区与集电区之间,只有耗尽区而无中性基区。

防止基区穿通的措施是提高WB与NB。

12. 基区发生大注入会对器件的注入效率、基区输运系数产生什么样的影响?

不管基区掺杂是否均匀,基区少子电流从形式上看好像完全由扩散电流构成,与均匀基区晶体管小注入时的情况相同,只是扩散系数D_B扩大了一倍。这就是Webster效应。扩散系数的加倍导致渡越时间的减半。

对于缓变基区晶体管,当n<2.56时,大注入使渡越时间缩短; 当n>2.56 时,大注入使渡越时间延长。

当发生大注入后, y随I_C增加而下降。

13. 简述基区扩展效应的机理。

当集电结电压不变、集电极电流增加时,基区宽度会展宽。

根据电流密度方程,在一定的电流密度下,当载流子的浓度为零时,其漂移速度应当为无穷大。但是实际上,不管集电结势垒区中的电场强度有多高,载流子的漂移速度也是有限的,最大只能达到饱和漂移速度,所以载流子浓度不可能为零。当载流子以一定的浓度和一定的速度越过势垒区时,载流子的电荷会对势垒区中的电场分布产生影响,其重要后果之一,就是当电流很大时,中性基区会变宽。

基区扩展的机理有两种,强电场下的基区扩展与弱电场下的基区扩展。

14. 简述发射结电流集边效应的机理。

当晶体管的工作电流很大时,基极电流通过基极电阻产生的压降也就很大,这会使得发射极电流在发射结上的分布极不均匀。实际上发射极电流的分布是离基极接触处越近电流越大,离开基极接触处较远的地方电流很快下降到很小的值。

15. 论述小信号电流从ie到ic的变化。

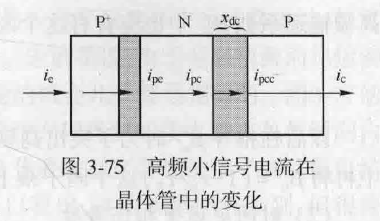

高频小信号电流从流入发射极的i_e到流出集电极的i_c,主要经历四个阶段的变化。第一次变化是从i_c变到注入基区的少子电流i_pe。i_pe与i_c相比,除了要减少从基区注入发射区的少子形成的心这部分电流外,还要受发射结势垒电容C_TE的作用而发生相应的变化。i_pe渡越过基区到达集电结边缘时变成i_pc。i_pc与i_pe相比,除了要减少在基区中因复合而损失掉的部分外,还要受发射结扩散电容C_DE的作用而发生相应的变化。由于集电结势垒区较厚,对高频电流有一定影响,使i_pc在越过集电结势垒区后变成i_pcc 。最后,i_pcc在受到集电结势垒电容C_TC 的作用后变i_c从集电极流出。

高频小信号电流从流入发射极的i_e到流出集电极的i_c,主要经历四个阶段的变化。第一次变化是从i_c变到注入基区的少子电流i_pe。i_pe与i_c相比,除了要减少从基区注入发射区的少子形成的心这部分电流外,还要受发射结势垒电容C_TE的作用而发生相应的变化。i_pe渡越过基区到达集电结边缘时变成i_pc。i_pc与i_pe相比,除了要减少在基区中因复合而损失掉的部分外,还要受发射结扩散电容C_DE的作用而发生相应的变化。由于集电结势垒区较厚,对高频电流有一定影响,使i_pc在越过集电结势垒区后变成i_pcc 。最后,i_pcc在受到集电结势垒电容C_TC 的作用后变i_c从集电极流出。

16. 简述基区渡越时间的三个作用。

复合损失使β0*小于1;时间延迟使相位滞后;渡越时间的分散使|βomega|减小。

17. 写出高频小信号作用下 BJT 的信号延迟时间并解释各部分的含义。

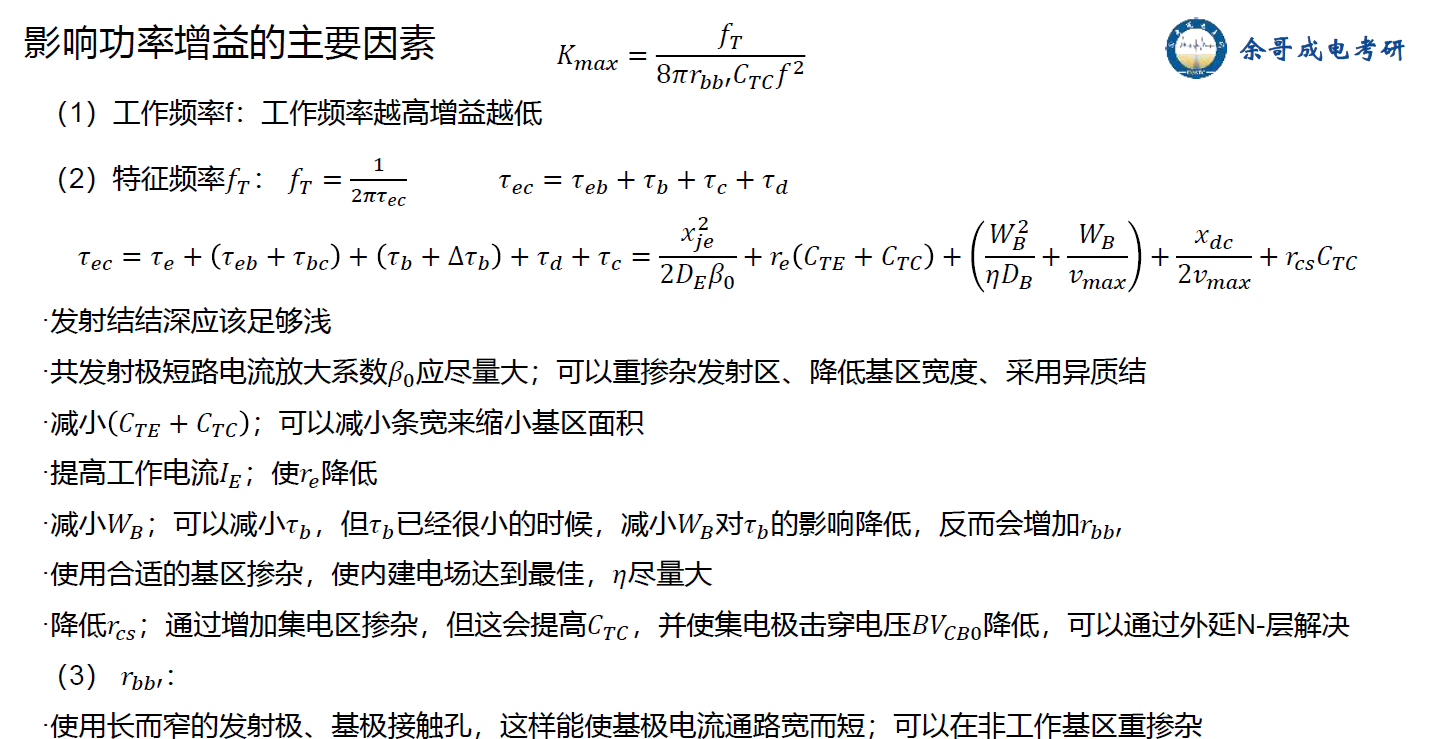

18. 怎样提高晶体管的高频特性/高频优值/高频晶体管的结构要求?

MOSFET

1. MOSFET 相比 BJT 有哪些好处?

(1) 输入阻抗高,这有利于各级间的直接耦合,有利千在大功率晶体管中将各子晶体管并接,有利于输入端与微波系统的匹配。

(2) 温度稳定性好。

(3) 噪声较小。

(4) 在大电流情况下跨导基本上不下降。

(5) 没有少子存储效应,因此开关速度快。

(6) 功耗低。

(7) 制造工艺简单。

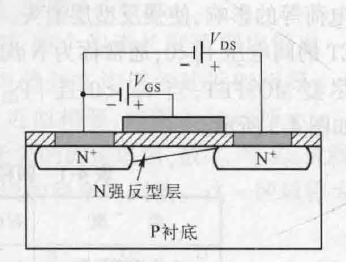

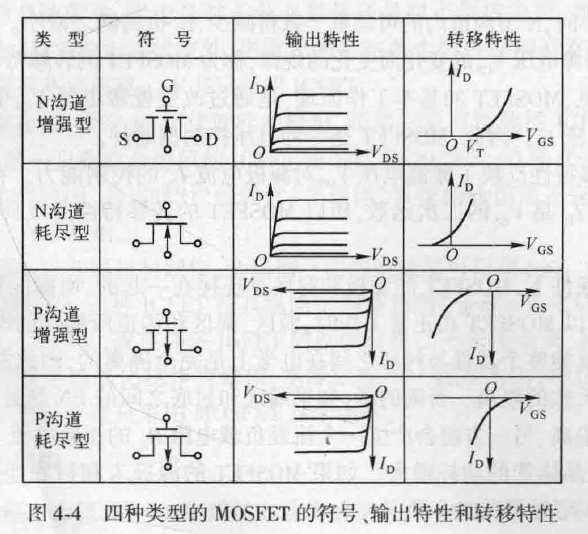

2. 简述 MOSFET 的工作原理。

MOSFET的工作原理是通过改变栅源电压𝑉_𝐺𝑆来控制沟道的导电能力,从而控制漏极电流𝐼_𝐷。

在N沟道MOSFET 中,当栅极上没有外加适当的栅极电压时,N+源区和N+漏区被两个背靠背的二极管所隔离。这时如果在漏极与源极之间加上漏源电压,除了极其微小的PN结反向电流外,是不会产生电流的。当在栅极上加上适当的电压栅源电压时,就会在栅极下面产生一个指向半导体体内的电场。当栅源电压增大到被称为阈电压的值时,由于电场的作用,栅极下面的P型半导体表面开始发生强反型,形成连通N+源区和N+漏区的N型沟道。由千沟道内有大量的可动电子,所以当在源极和源极之间加上漏源电压后,就能产生漏极电流。

3. 什么是MOSFET的阈电压、阈电压由哪些部分组成、怎样调节阈值电压?

对于NMOSFET,当注入杂质与衬底杂质的类型相同时,N沟道MOSFET的阈电压向正向调整;当注入的是对衬底起补偿作用的杂质时,N沟道MOSFET的阈电压向负向调整。

对于NMOSFET,当注入杂质与衬底杂质的类型相同时,N沟道MOSFET的阈电压向正向调整;当注入的是对衬底起补偿作用的杂质时,N沟道MOSFET的阈电压向负向调整。

对于PMOSFET,当注入杂质与衬底杂质的类型相同时,P沟道MOSFET的阈电压向负向调整;当注入的是对衬底起补偿作用的杂质时,P沟道MOSFET的阈电压向正向调整。

4. 什么是阈电压的衬底偏置效应?

衬底与源极之间外加衬底偏压后, MOSFET的特性将发生某些变化。栅氧化层厚度Tox越厚,衬底杂质浓度越高, 则体效应就越严重。

对于P沟道MOSFET,随着衬底偏置电压的增大,转移特性曲线向左平移,说明阈电压向负方向移动,或阈电压的绝对值增大。(N右)

5. 推导MOSFET直流电流电压方程时做了哪些假设?

(1) 沟道内的电流完全由漂移电流构成,忽略扩散电流。

(2) 采用缓变沟道近似,即认为垂直于沟道方向的电场梯度远大于平行于沟道方向的电场梯度,这表示沟道厚度在沿沟道长度方向上的变化很小,故可采用一维分析。从泊松方程可知,实际上意味着沟道内的载流子电荷都是由栅极电压所感应出来的,而可忽略由漏极电压作用。

(3) 沟道内的电子迁移率为常数。

(4) 采用强反型近似,即认为当半导体表面的反型层电子浓度达到体内平衡空穴浓度时,沟道才开始导电。

(5) 栅氧化层内的有效电荷面密度Qox为常数,并与能带的弯曲程度无关。

6. 饱和区漏极电流不饱和的原因有哪两种?具体机理分别是什么?

有效沟道长度调制效应,当发生夹断时,𝑉 𝐷𝑆中大于𝑉 𝐷 𝑠𝑎𝑡的部分降落在夹断点右边的夹断区域Δ 𝐿上,看做漏PN结的耗尽区当L越小时,Δ 𝐿带来的影响越显著,且𝑁 𝐴越小,Δ 𝐿越大,有效沟道长度调制效应越显著。

漏区静电场对沟道区的负反馈作用,制作在较低掺杂浓度衬底上的MOSFET ,当𝑉 𝐷𝑆大于𝑉 𝐷 𝑠𝑎𝑡, 其漏区附近的耗尽区较宽,严重时甚至可以与有效沟道长度相比拟,在沟道长度较短时尤为显著。这时起始于漏区的电力线中的部分将穿过耗尽区而终止于沟道,耗尽区内的电场强度随之增强,使沟道内的电子数也相应增加,以终止增多的电力线。

在衬底为中等或较高掺杂浓度的MOSFET中,使饱和区漏极电流不饱和的主要原因是有效沟道长度调制效应,而在衬底掺杂浓度较低的MOSFET中,则以漏区与沟道间的静电耦合作用为主。

7. 简述亚阈区对应的电压范围、表面势范围、应用场景,什么是亚阈区摆幅?

当栅源电压在V_i<V_GS<V_T范围内时,表面势介于φFp和φ2Fp之间,表面处于弱反型状态,表面电子浓度介于本征载流子浓度和衬底平衡多子浓度之间。

亚阈区在MOSFET的低压低功耗应用中,以及在数字电路中用做开关或者存储器时,有很重要的意义。

亚阈区转移特性的半对数斜率的倒数称为亚阈区栅源电压摆幅,记为S。

亚阈区转移特性的半对数斜率的倒数称为亚阈区栅源电压摆幅,记为S。

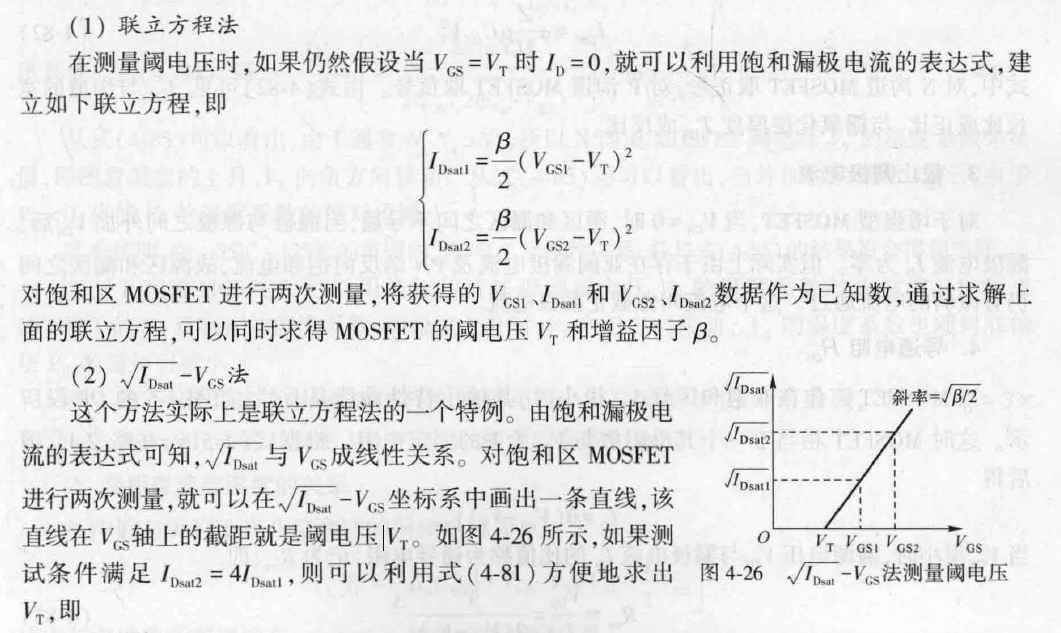

8. 阈电压测量方法。

9. 推导NMOS阈电压的温度系数、推导漏极电流的温度系数。

10. MOSFET为什么有好的温度稳定性?

当MOSFET的工作条件满足时, I_D将不随温度的变化而变化。因此只要适当选择工作条件, MOSFET就会有很高的温度稳定性。此外, 当VGS -VT较大时,也即I_D较大从而功耗较大时,I_D的温度系数为负,这也有利于MOSFET的温度稳定性。

11. 为什么MOSFET比PN结更容易发生雪崩击穿?

由金属栅极引起的附加电场的影响。MOSFET 的金属栅电极一般覆盖了漏区边缘的一部分。如果金属栅极的电势低于漏区的电势,就会在涌区与金属栅极之间形成一个附加电场。这个附加电场使栅极下面漏PN结耗尽区中的电场增大,因而击穿首先在该处发生。

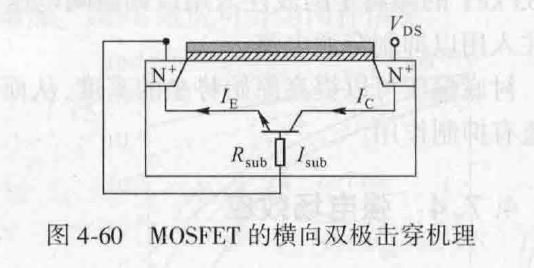

12. 为什么MOSFET比BJT更容易发生穿通?

在双极型晶体管中,基区掺杂浓度高于集电区,集电结耗尽区主要向集电区扩展,一般不易发生基区穿通。而在MOSFET中,由于漏区掺杂浓度高于衬底,耗尽区主要向衬底扩展,所以MOSFET的漏源穿通问题比双极型晶体管的基区穿通要严重得多。

13. 怎样提高MOSFET的最高工作频率?

为了提高最高工作频率, 一方面,应选用迁移率大的N沟道器件,缩短沟道长度L,提高栅源电压。另一方面,应减小寄生电容,即采用自对准工艺。

14. 什么是阈电压的短沟道效应?

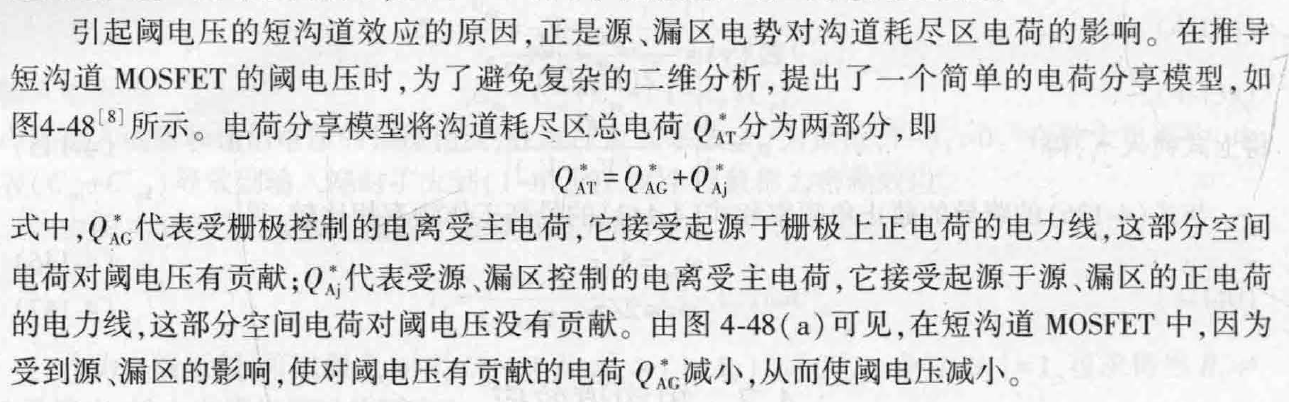

当MOSFET的沟道长度缩短到可以与源、漏区的结深相比拟时,阈电压将随沟道长度L的缩短而减小。这就是阈电压的短沟道效应。

15. 什么是阈电压的窄沟道效应?

当MOSFET的沟道宽度Z很小时,阈电压将随着Z的减小而增大。这个现象称为阈电压的窄沟道效应。

16. 简述迁移率调制效应。

𝑉 𝐺𝑆对u的影响:表面散射加强。

𝑉 𝐷𝑆对u的影响:速度饱和的影响。

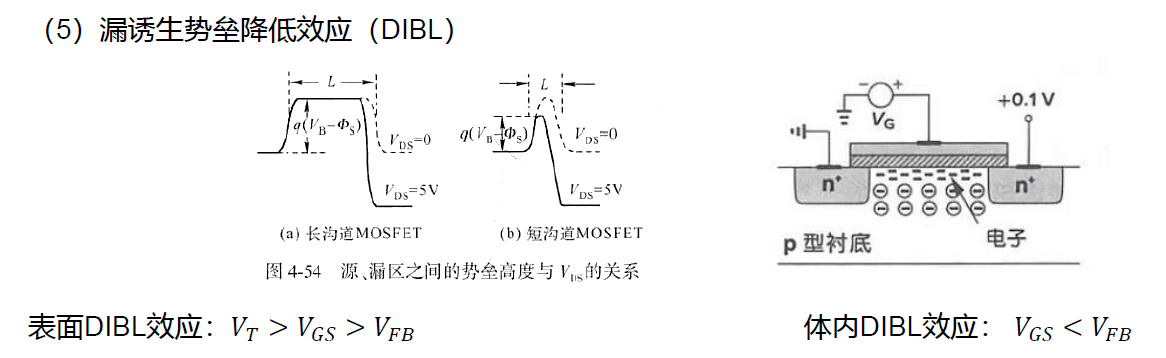

17. 简述DIBL效应。

以N沟道MOSFET为例, N+源区、P衬底和N+漏区形成了两个背靠背的二极管。漏源电压VDS对漏PN结为反偏。对千长沟道MOSFET,几乎全部降在漏PN结上,对源PN结没有什么影响。但在短沟道MOSFET中,由于沟道长度很短,起源于漏区的电力线将有一部分贯穿沟道区终止于源区,从而使源、湘区之间的势垒高度降低。

以N沟道MOSFET为例, N+源区、P衬底和N+漏区形成了两个背靠背的二极管。漏源电压VDS对漏PN结为反偏。对千长沟道MOSFET,几乎全部降在漏PN结上,对源PN结没有什么影响。但在短沟道MOSFET中,由于沟道长度很短,起源于漏区的电力线将有一部分贯穿沟道区终止于源区,从而使源、湘区之间的势垒高度降低。

表面DIBL效应,电子从源区向沟道的注入,以及电子在沟道内的流动,都发生在表面直到在漏区附近电子才稍向体内扩展,最后流入漏区,形成亚阈电流。

体内DIBL效应,电子从源区向沟道的注入,以及电子在沟道内的流动,都发生在体内,最后流入漏区,形成穿通电流,离子注入、外加衬底偏压可以抑制体内穿通电流。

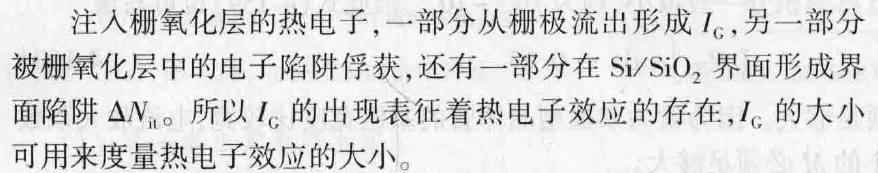

18. 热电子效应的来源、去处、不利影响、防治措施。

第一, 漏PN结采用缓变结,例如砷-磷(N+_N-) 双扩散结构或磷扩散区结构。第二,采用偏置栅结构。第三,采用埋沟结构。

第一, 漏PN结采用缓变结,例如砷-磷(N+_N-) 双扩散结构或磷扩散区结构。第二,采用偏置栅结构。第三,采用埋沟结构。

19. 简述恒场按比例缩小法则的局限性。

MOSFET的亚阈区摆幅S将与未缩小的基本相同。当MOSFET的工作电压减小时,恒定的S值会使亚阈电流相对增大,这对动态存储器特别不利。

某些电压参数不能按比例缩小。

表面反型层厚度b是一个不能按比例缩小的几何参数。

如果源、福区和金属互连线的长、宽、高都缩小到(1/K) , 则串联电阻将扩大K倍。

在实际电路中,考虑到与TTL电路与其他标准电路的兼容性,以及噪声容限方面的原因等,电源电压降到一定程度后难以继续下降。

20. 什么是多晶硅耗尽效应?

一直以来多晶硅都被看做良导体,其功函数由简并的N型硅和P型硅决定。然而实际上即使是重掺杂多晶硅,其载流子浓度上与金属存在着巨大差异,性能也和理想的导体不同。在MOS结构中加上栅压后,栅电极上的正电荷由多晶硅的电离杂质所提供,在栅氧化层不断减薄的情况下,多晶硅耗尽区厚度将达到纳米级,从而造成栅电容减小,必须考虑多晶硅耗尽效应的影响。多晶硅耗尽区将使其靠近二氧化硅界面有能带弯曲和耗尽层电荷分布,相当于增加了氧化层厚度,使有效栅压降低,还将使阈值电压上升,漏源电流降低。

21. 什么是速度过冲效应?

但是在深亚微米MOSFET中,由于器件中存在很大的电场梯度,以及沟道长度逐渐接近电子的平均自由程,则会出现速度过冲效应。当存在电场梯度时,在能量弛豫时间内电子速度可以超过对应于更高电场的速度值,电子开始与晶格处于不平衡状态。在电子的输运过程中不能发生足够的散射,从而导致电子被加速到超过饱和速度,这种现象称为速度过冲效应。漏极电流增大,跨导增大。

22. 简述限制栅氧化层厚度缩小的因素。

电子隧道效应:栅氧化层厚度低于2nm ,电子隧穿使得栅泄漏电流急剧增大。

量子效应:由于量子机制的作用,反型层电子浓度的峰值将离开界面。可以将该现象等效为栅氧化层厚度的增加。

多晶硅耗尽效应:多晶硅耗尽区将使其靠近二氧化硅界面有能带弯曲和耗尽层电荷分布,相当于增加了氧化层厚度。

表面反型层厚度b是一个不能按比例缩小的几何参数。

栅源击穿。

解决:高K栅介质及金属栅电极MOSFET。采用高K材料以后,在保持相同的单位面积栅电容,从而保证对沟道有相同控制的条件下,栅绝缘介质介电常数的增加将使栅介质层的物理厚度TK增大,于是栅与沟道间的直接隧穿电流将大大减小;采用合适的金属来取代以避免多晶硅耗尽效应。

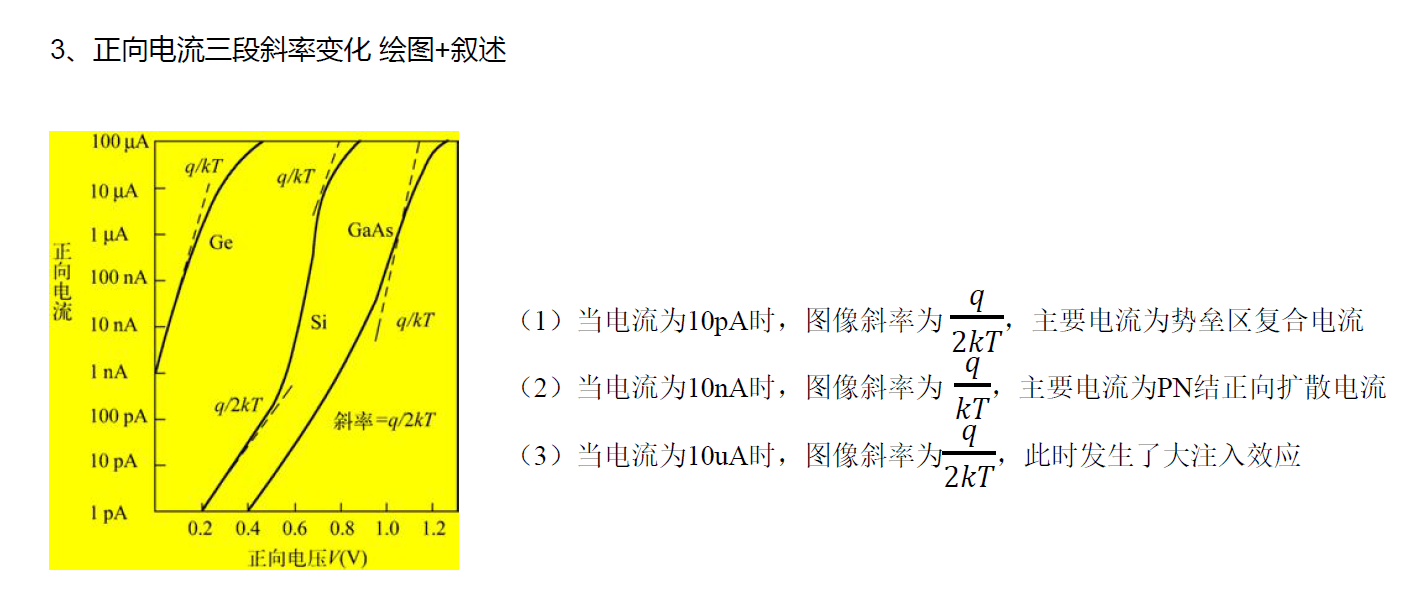

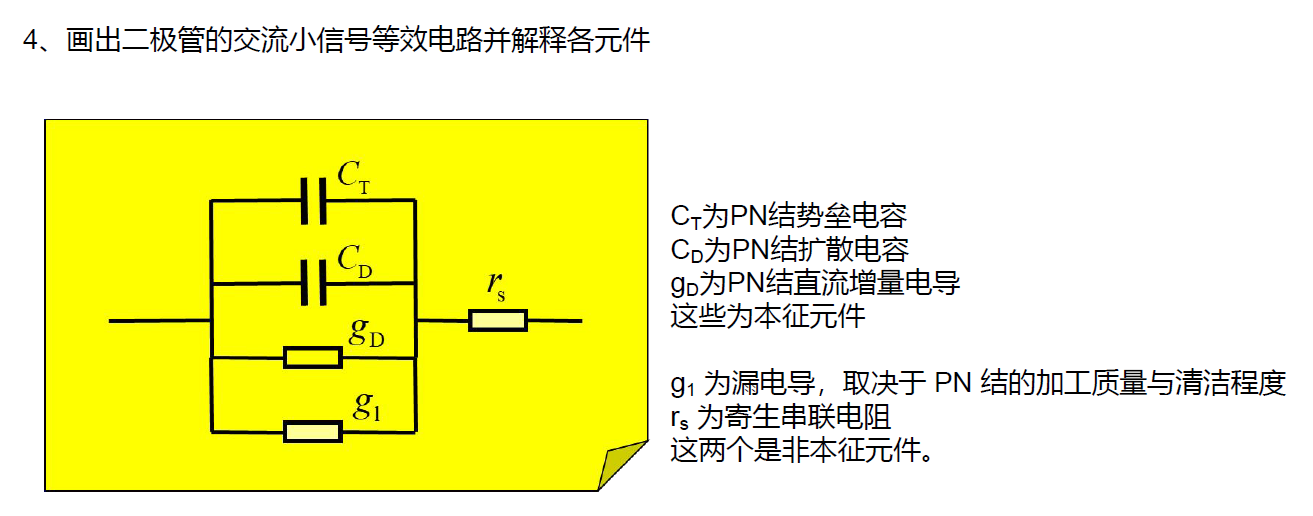

作图题